Intel终于要挤出10nm 智能驾驶企业却纷纷选择28nm

近日,芯片巨头Intel终于宣布其10nm芯片有望在2019年下半年开始出货。

摩尔定律发展到今天已经失效,这些年来,Intel在10nm工艺制程上一直发展不顺利,近乎难产,以至于从2015年发布Skylake架构芯片以来,该公司一直在14nm工艺上修修补补,甚至有传言称Intel内部已完全放弃10nm计划。

所幸,Intel宣布明年将推出下一代Sunny Cove架构的酷睿(Core)与至强(Xeon)芯片。

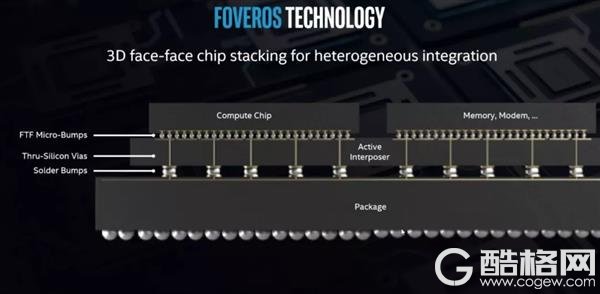

据了解,Sunny Cove是一种基于10nm工艺构建的增强型微架构,但Intel推出的并非是完全体的10nm芯片,而是通过Foveros技术将不同性能、不同部分封装在一起,仅高性能部分使用10nm工艺制程。

Foveros是一种逻辑芯片3D堆叠技术,之前已经应用在存储芯片上,但用在CPU上仍有困难。Foveros技术允许将复杂的逻辑芯片堆叠在一起,从而提供更大的功能,使处理器不同部分的组件与相应的制造工艺匹配。

例如,高性能CPU内核可能构建在性能最高的10nm工艺上,但集成USB、Wi-Fi、以太网、PCIe的I/O连接部分不需要这么高的性能,采用14nm甚至22nm工艺可能更有意义,因为其性能足够,但功耗和成本要低得多。

Foveros意味着处理器可以按照不同的制程集成这些组件,这些不同的组件可以并排紧密包装在一起,实现更高的密度和更小的芯片面积。

芯片在完成前期的设计和开发之后,将交由芯片代工厂进行流片,再往后便是封装和批量生产。目前,比较知名的芯片代工厂包括Intel、三星、台积电以及格罗方德这样的公司。

自1995年以后,半导体制程工艺水平从500nm、350nm、250nm一直进化到如今的28nm、10nm以及7nm。目前,多数代工厂都在大力投入7nm生产线,相关的样片也已经流片成功。

所谓制程纳米,是CMOSFET晶体管闸极的宽度,即闸长。闸长可以分为光刻闸长和实际闸长。由于在光刻中光存在衍射现象以及芯片制造中还要经历离子注入、蚀刻、等离子冲洗、热处理等步骤,因此会导致光刻闸长和实际闸长不一致的情况。

另外,同样的制程技术下,实际闸长也会不一样。Intel在10nm制程上与对手进行的以下对比便足以说明问题。

闸长越短,有两大好处:一是提高晶体管密度,在同样大小的硅晶圆制造更多的晶体管,运算能力会更强;另一个好处是降低功耗,因为闸长决定了电流通过时的损耗,宽度越窄,功耗越低。

这也是为什么众多芯片设计商要采用更先进的制程工艺的原因,但将真实需求、投入成本、技术成熟度引入进考量体系的话,很多芯片设计企业并不会一味去追求最新的制程工艺,他们会选择在具体时间节点上性价比最高的工艺。

根据咨询公司Gartner的推算,10nm芯片的总设计成本约为1.2亿美元,7nm芯片则为2.71亿美元,较10nm高出两倍之多,所以并不是所有企业都能追逐最新的工艺。

智能驾驶芯片企业所选择的芯片制程工艺在12nm-40nm之间,策略是比较稳妥而且保守的。

调研结论显示,芯片制程工艺的发展所推动的性能提升与成本下降两大趋势在28nm工艺节点发生转折,再往更先进的工艺做,成本不降反升。从商业上考量,对于一些民用的场景,比如智能汽车,28nm是性价比最好的一代技术。

2018年年初,全球领先的芯片代工厂台积电宣布保留28nm工艺生产线,作为长周期、长寿命的技术,这代技术最稳定,而且应用也非常广泛。虽然目前的技术已经进化至7nm,甚至是5nm。

当大厂和创业公司同时选择一家芯片代工厂之时,未来相应的订单生产优先级也将产生一定的差异,好在目前这些企业选择的芯片制程工艺重合度还没那么高。

相关企业在接受调研时表示,以台积电为例,他们在行业中还是很讲规则的,要在台积电进行芯片的流片和量产,需要申请一系列资质,包括企业背景、技术以及产品未来的预测,同时对方还会来企业内部做调查,最后才能确定是否为该企业开辟账户。

iOS 13.4正式版升级体验:信号提升、更

iOS 13.4正式版升级体验:信号提升、更 90年代热血回忆 小米有品开卖NEOGEO M

90年代热血回忆 小米有品开卖NEOGEO M 微软提高Win10稳定性:部分用户先当小

微软提高Win10稳定性:部分用户先当小 绿米联创与Sonos达成战略合作,打造全

绿米联创与Sonos达成战略合作,打造全 日本推10Gbps万兆宽带:月费约380元

日本推10Gbps万兆宽带:月费约380元 小爱同学定制声音、定制唤醒词,震撼

小爱同学定制声音、定制唤醒词,震撼